## 100MSPS 2ch Digitizer Board for PCI **DIG-100M1002-PCI**

\* Specifications, color and design of the products are subject to change without notice.

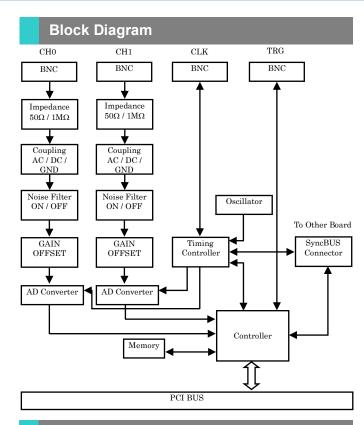

This product is a PCI-bus compliant digitizer board. It is designed with the following features:

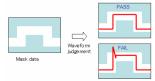

10-bit resolution, up to 100MSPS (10nsec) conversion speed, sampling 2 channels simultaneously. In addition, it features with the PASS/FAIL judgment functionality by comparing input data with the set standard data (mask data) one by one. The large (32M data) on-board memory and bus master transfer function allow continuous data acquisition to be performed at high speed for a long period.

The automation of the measurement is facilitated by factors such as various sampling control and waveform judgment function based on mask data.

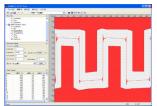

The mask editor software is attached as a tool to generate comparison waveform data. You can create the waveform data by drawing on screen directly with mouse or drawing with mathematics functions (input numerical values). Moreover, you can make use of the supplied front panel soft as an oscilloscope or a waveform judgment instrument. In addition, Windows API is also supplied, so that you can also program in Visual Baisc or Visual C++.

#### **Features**

## Free yourself from visual inspection. The inspected input signal can be automatically judged whether OK or NG.)

By comparing the sampled signal waveform with the pass range which is set beforehand, a pass or fail judgment can be done automatically with the waveform level.

It is intended to not only save labor on present visual examination greatly but also improve/uniform the quality. Moreover, the "Mask Editor Software" is supplied as a tool to create comparison waveform data and is Windows exclusive use, by which the following operation can be done, drawing on screen directly/drawing straight line/sine wave with mouse, drawing constant voltage/ square wave/triangular wave/step//ramp/sawtooth wave with mathematics functions.

# "Front panel software" is supplied that can be used as the oscilloscope or the waveform judgement instrument easily.

The "Front Panel Software", an application that makes an image of oscilloscope or waveform judgment instrument, is supplied. You can use it easily with no need of programming.

Moreover, you can use it to check the configured execution environment, because it features the functionality of diagnosing and reporting the status of the board and device driver.

# Resolution 10bits, maximum conversion speed is 10MSPS (100nsec), with simultaneous sampling of 2channels at a time

A 10bits high-speed A/D covonverter is used, the measurement at the highest conversion speed of 100MSPS(10nsec) is possible. It is possible to sample 2 channels simultaneously. Moreover, it is equipped with a mass on-board memory of 32M data that archieves continuous sampling, regardless of the processing performance of the PC. It is also equipped with bus master transfer function by which the sampling data is transferred to PC memory with high speed.

A variety of settings for signal input such as impedance, range, filter and coupling can be performed.

Analog input channel's input impedance can be selected between  $50\Omega$  and  $1M\Omega$ . The measurement using a general-purpose passive probe is also possible by  $1M\Omega$ . According to the voltage level of signal source connected, a number of ranges can be switched (When  $1M\Omega$  is set, there are 10 ranges between  $40mVpk[\pm 20mV]$  and  $40Vpk[\pm 20V]$ . When  $50\Omega$  is set, there are 8 ranges between  $40mVpk[\pm 20mV]$  and  $10Vpk[\pm 5V])$ , so that you can make good use of the 10bit resolution. By enabling the noise filter (low pass filter: 20MHZ), it is possible to perform the measurement with reducing the influence of mixed high frequency noise from signal source and ambient environment.

The input coupling can be selected from AC/DC/GND. (AC is only available when  $1M\Omega$  is set.)

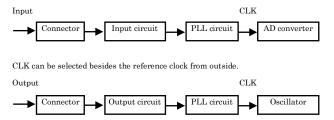

## The synchronization between external instrument and the board is possible with the reference clock I/O.

The synchronization between other measuring instrument or another board with the same type becomes easily for that the reference clock (10MHz) can be input/output.

It is possible to expand the number of channels by the synchronization between another board with the same type, and measure the mixed signal by the synchronization between other measuring instrument..

# Sampling can be controlled by software, conversion data comparison, external trigger, event controller output, and similar start and stop conditions

Sampling can be setup to be started and stopped by software, conversion data comparison, external trigger, or event controller output. Control of sampling start and stop is completely independent and a separate setting is provided for each. It is also possible to specify that sampling stop after a specified number of samples. There are two kinds of comparison for conversion data. The one is implemented by comparing the conversion data edge (rising edge, falling edge or both edges), the other one is implemented by window trigger that is satisfied when conversion data go inside/outside a certain boundary.

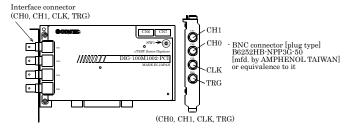

### BNC connector used for analog input, trigger and reference clock

The BNC connector used for the connector has a characteristic impedance of  $50\Omega$  and is of a type commonly used for high speed analog signal.

#### The function of saving/reading configuration file and auto setup for sampling condition

The work time of setup can be greatly shortened for that acquisition conditions such as horizontal axis setting, vertical axis setting and trigger setting can be save/read into/from a file. Moreover, it is equipped with the auto setup function that scans input signals of each channel and then performs settings automatically. By configuration software, it is possible to create a configuration file of acquisition conditions or edit an existing file in a wizard form. The created file can be read by front panel software or from the program using API-PAC(W32) cTEST.

#### Windows compatible driver library API-PAC(W32) cTEST is attached.

Using the attached driver library makes it possible to create applications of Window.

#### **Specification**

#### Specification < 1/3>

| Item                                    | Item Specification                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Analog input channels specification     |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Isolated specification                  | Non-isolated                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Type                                    | Single-Ended Input                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Number of input channels                | 2ch Synchronized Sampling                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Input impedance *1                      | You can select 1M $\Omega$ ±1% // 19pF typ. or 50 $\Omega$ ±2%                                                                                                                                                                                                                                                                                     |  |  |  |

| Input coupling                          | AC, DC, GND (AC coupling can be used only when $1M\Omega$ is set.)                                                                                                                                                                                                                                                                                 |  |  |  |

| Input voltage range                     | < When input impedance 1MΩ is set. > 40mVpk [±20mV], 100mVpk [±50mV], 200mVpk [±100mV] 400mVpk [±200mV], 1Vpk [±500mV], 2Vpk [±1V], 4Vpk [±2V], 10Vpk [±5V], 20Vpk [±10V], 40Vpk [±20V] < When input impedance 50Ω is set. > 40mVpk [±20mV], 100mVpk [±50mV], 200mVpk [±100mV] 400mVpk [±20mV], 1Vpk [±500mV], 2Vpk [±1V], 4Vpk [±2V], 10Vpk [±5V] |  |  |  |

| Offset range setting                    | Input voltage range's ±50%<br>(For 1MQ:40Vpk, 50Q:10Vpk: ±0%)                                                                                                                                                                                                                                                                                      |  |  |  |

| Max.input voltage *2                    | When input impedance $1M\Omega$ is set.<br>$\pm 30 VDC$ (Max.)<br>When input impedance $50\Omega$ is set.<br>$\pm 5.6 VDC$ (Max.)                                                                                                                                                                                                                  |  |  |  |

| Resolution                              | 10bit                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Conversion speed *3                     | 100MHz (10nsec) Max.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Frequency bandwidth (-3dB)              | 60MHz typ.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Noise filtering<br>bandwidth<br>(-3dB)  | 20MHz typ. Attenuation property: Low-Pass Filter                                                                                                                                                                                                                                                                                                   |  |  |  |

| AC coupling cut off<br>frequency (-3dB) | 13Hz typ.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| On-board memory                         | 32M data                                                                                                                                                                                                                                                                                                                                           |  |  |  |

- Switch to  $1M\Omega$  automatically when power is turned off. Do not input a voltage over the Max. input voltage.

#### Specification < 2 / 3 >

| Item                              | . 213/                                                                                                                                                                                            | Sn                       | ecification                            |                            |                |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|----------------------------|----------------|--|

|                                   | Specification                                                                                                                                                                                     |                          |                                        |                            |                |  |

| Analog input channel meas         |                                                                                                                                                                                                   | n                        |                                        |                            |                |  |

| DC conversion<br>precision *4*5*6 | Within ±0.4%<br>(Input voltage range : 400mVpk, 1Vpk, 2Vpk, 4Vpk, 10Vpk, 20Vpk, 40Vpk)<br>Within ±0.6%<br>(Input voltage range : 100mVpk,200mVpk)<br>Within ±1%<br>(Input voltage range : 40mVpk) |                          |                                        |                            |                |  |

| Non-Linearity error<br>*4*5*6     | Within ±0.3%                                                                                                                                                                                      |                          |                                        |                            |                |  |

| Offset/range setting precision    | ±0.3% of range                                                                                                                                                                                    |                          |                                        |                            |                |  |

| Amplitude flatness                | DC · 10MHz : ±0.3dB typ.                                                                                                                                                                          |                          |                                        |                            |                |  |

| (based on 1kHz) *7                | 10MHz - 30MHz : ±1dB typ.                                                                                                                                                                         |                          |                                        |                            |                |  |

| Cross talk                        | Between analog<br>Reference clock<br>channels<br>When input vol<br>Input voltage ra                                                                                                               | / trigger I/0 tage range | O → Betwee<br>40mV is set<br>than 40mV | .: 60dB typ<br>: 70dB typ. | ·<br>·         |  |

|                                   | When input impedance $50\Omega$ is set (test signal: 10MHz, -1dBFS) typ.                                                                                                                          |                          |                                        |                            |                |  |

|                                   | Voltage range                                                                                                                                                                                     | SNR                      | THD                                    | SFDR                       | SINAD          |  |

|                                   | 40mV                                                                                                                                                                                              | 53 dB                    | -68 dBc                                | 71 dBc                     | 53 dB          |  |

|                                   | 100mV                                                                                                                                                                                             | 58 dB                    | -73 dBc                                | 76 dBc                     | 58 dB          |  |

|                                   | 200mV                                                                                                                                                                                             | 60 dB                    | -72 dBc                                | 74 dBc                     | 60 dB          |  |

|                                   | 400mV<br>1V                                                                                                                                                                                       | 59 dB<br>60 dB           | -75 dBc<br>-72 dBc                     | 78 dBc<br>76 dBc           | 59 dB<br>60 dB |  |

|                                   | 2V                                                                                                                                                                                                | 60 dB                    | -72 dBc                                | 76 dBc                     | 60 dB          |  |

|                                   | 4V                                                                                                                                                                                                | 60 dB                    | -75 dBc                                | 78 dBc                     | 59 dB          |  |

|                                   | 10V                                                                                                                                                                                               |                          |                                        |                            |                |  |

| Spectrum property *7              | When input impedance $1M\Omega$ is set (test signal: $10MHz$ ,                                                                                                                                    |                          |                                        |                            |                |  |

| Spectrum property                 | Voltage range                                                                                                                                                                                     | SNR                      | THD                                    | SFDR                       | SINAD          |  |

|                                   | 40mV                                                                                                                                                                                              | 42 dB                    | -50 dBc                                | 51 dBc                     | 42 dB          |  |

|                                   | 100mV                                                                                                                                                                                             | 50 dB                    | -59 dBc                                | 61 dBc                     | 50 dB          |  |

|                                   | 200mV                                                                                                                                                                                             | 56 dB                    | -62 dBc                                | 65 dBc                     | 55 dB          |  |

|                                   | 400mV                                                                                                                                                                                             | 58 dB                    | -67 dBc                                | 68 dBc                     | 58 dB          |  |

|                                   | 1V                                                                                                                                                                                                | 60 dB                    | -71 dBc                                | 74 dBc                     | 60 dB          |  |

|                                   | 2V                                                                                                                                                                                                | 53 dB                    | -76 dBc                                | 78 dBc                     | 53 dB          |  |

|                                   | 4V                                                                                                                                                                                                | 57 dB                    | -74 dBc                                | 75 dBc                     | 57 dB          |  |

|                                   | 10V                                                                                                                                                                                               | 59 dB                    | -73 dBc                                | 76 dBc                     | 59 dB          |  |

|                                   | 20V                                                                                                                                                                                               | -                        | -                                      | -                          | -              |  |

|                                   | 40V                                                                                                                                                                                               | -                        | -                                      | -                          | -              |  |

|                                   |                                                                                                                                                                                                   |                          |                                        |                            |                |  |

| Time based accuracy               | When on board crystal oscillator is set (default)<br>±5ppm (Temperature drift:±2.5ppm(0 · 50°C),<br>Aging:±1ppm/year)<br>When synchronize with external reference clock                           |                          |                                        |                            |                |  |

|                                   | Depending on the accuracy of external reference clock                                                                                                                                             |                          |                                        |                            |                |  |

- The designated precision may not be satisfied because of cable. Voltage generator R6161 [ADVANTEST] is used in measurement. It is the value when offset/range is set to 0V.

- It may cause failure. When 2ch are used, the Max. conversion speed is 50MHz (when data logger mode is

#### Specification < 3 / 3 >

| Item                                               | Specification                                                                                                            |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Reference clock I/O                                |                                                                                                                          |  |  |  |

| Input frequency                                    | 10MHz (Duty cycle is within 50±5%) *8                                                                                    |  |  |  |

| Input impedance                                    | 600Ω                                                                                                                     |  |  |  |

| Input coupling                                     | AC                                                                                                                       |  |  |  |

| Input voltage                                      | 0.2Vpk - 3.3Vpk                                                                                                          |  |  |  |

| Max.input voltage                                  | ±5V                                                                                                                      |  |  |  |

| Output frequency                                   | 10MHz                                                                                                                    |  |  |  |

| Output impedance                                   | 50Ω                                                                                                                      |  |  |  |

| Output coupling                                    | DC                                                                                                                       |  |  |  |

| Output voltage                                     | When $50\Omega$ terminal resistance is used : 1V $$ When open : $2V$                                                     |  |  |  |

| Output frequency accuracy                          | ±5ppm (aging: ±1ppm/year)                                                                                                |  |  |  |

| External trigger I/O                               |                                                                                                                          |  |  |  |

| Logic type                                         | 3.3V LVTTL                                                                                                               |  |  |  |

| Output impedance                                   | $50\Omega$                                                                                                               |  |  |  |

| I/O coupling                                       | DC                                                                                                                       |  |  |  |

| I/O signal                                         | Trigger, general-purpose digital signal                                                                                  |  |  |  |

| Trigger system                                     |                                                                                                                          |  |  |  |

| source                                             | CH0, CH1, software, trigger input, synchronous control connector                                                         |  |  |  |

| Conversion start<br>trigger                        | Software, conversion data compare, external trigger, and event controller output.                                        |  |  |  |

| Conversion stop trigge                             | r Settings include data save complete, conversion data compare, external trigger, event controller output, and software. |  |  |  |

| External start signal                              | LVTTL level (Rising or falling edge can be selected by software)                                                         |  |  |  |

| External stop signal                               | LVTTL level (Rising or falling edge can be selected by software)                                                         |  |  |  |

| External status output                             | LVTTL level Sampling clock output                                                                                        |  |  |  |

| Bus master section                                 |                                                                                                                          |  |  |  |

| DMA channels                                       | 1channel                                                                                                                 |  |  |  |

| Transfer bus width                                 | 32bit                                                                                                                    |  |  |  |

| Transfer data length                               | 8 PCI data length (Max.)                                                                                                 |  |  |  |

| FIFO                                               | 1K data                                                                                                                  |  |  |  |

| Scatter/Gather                                     | 64M-Byte                                                                                                                 |  |  |  |

| function                                           |                                                                                                                          |  |  |  |

| Synchronization bus section  Control output signal | Selection of output signal with the software when                                                                        |  |  |  |

| Control output signal                              | master board.                                                                                                            |  |  |  |

| Control input signal                               | Selection of sync factor with the software when specifying sync slave boards.                                            |  |  |  |

| Max. board count for connection                    | 16 boards including the master board                                                                                     |  |  |  |

| Connector                                          | PS-10PE-D4LI-B1 (mfd. By JAE) or equivalence to it x 2                                                                   |  |  |  |

| Common                                             | T                                                                                                                        |  |  |  |

| I/O address                                        | 64 ports x 1, 256 ports x 1 region                                                                                       |  |  |  |

| Interrupt level                                    | Errors and various factors, One interrupt request line as INTA                                                           |  |  |  |

| Connector used                                     | BNC (Characteristic Impedance $50\Omega$ )                                                                               |  |  |  |

| Currrent consumption                               | 5VDC 1.9A (Max.), 3.3VDC 0.1A (Max.)                                                                                     |  |  |  |

| Operating condition                                | 0 - 50°C, 10 - 90%RH (No condensation)                                                                                   |  |  |  |

| Bus specification                                  | PCI (32bit, 33MHz, Universal key shapes supported *9)                                                                    |  |  |  |

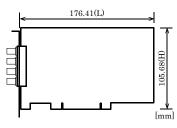

| Dimensions (mm)                                    | 176.41(L) x 105.68(H)                                                                                                    |  |  |  |

| Weight<br>Standard                                 | 400g  VCCI Class A, CE Marking (EMC Directive Class A, RoHS                                                              |  |  |  |

|                                                    | Directive), UKCA                                                                                                         |  |  |  |

If the accuracy for the externally input clock is worse than the accuracy listed in time based accuracy, this product acquires the data 1.3 us (max) before the external trigger signal was input when external trigger signal input was used for the pre-/post-trigger \*9: This product requires +5V and +3.3V power supply from expansion slots.

#### **Board Dimensions**

The standard outside dimension (L) is the distance from the end of the board to the outer surface of the slot cover.

#### **Support Software**

#### Windows version of digitizer driver API-DIG(WDM) [Stored on the bundled CD-ROM driver library API-PAC(W32) cTEST]

The API-DIG(WDM) is the Windows version driver library software that provides products in the form of Win32 API functions (DLL). Various sample programs such as Visual Basic and Visual C++, etc is provided.

#### Windows version of application software Front panel software

#### [Stored on the bundled CD-ROM driver library API-PAC(W32) cTEST]

The front panel software is an application which can be used as an oscilloscope or waveform judgment instrument, it also has the function of diagnosing the state of the board and its driver. Moreover, you may use the "Diagnosis Report" feature reports the driver settings, the presence or absence of the board, I/O status, and interrupt status.

#### Windows version of application software Configuration software

#### [Stored on the bundled CD-ROM driver library API-PAC(W32) cTEST]

By configuration software, you may create a configuration file of acquisition conditions for this product in a wizard form.

#### Windows version of application software Mask editor software

#### [Stored on the bundled CD-ROM driver library API-PAC(W32) cTEST]

By the mask editor software, you may create a configuration file for waveform judgment with creating the waveform by drawing on screen directly with mouse or drawing with mathematics functions.

For more details on the supported OS, applicable language and how to download the updated version, please visit the CONTEC's Web site.

#### **Cable & Connector**

#### Cable (Option)

**BNC Cable**

- : BNC-B100 (1m), BNC-B200 (2m), BNC-B300 (3m)

- Check the CONTEC's Web site for more information on these options.

#### **Packing List**

Board [DIG-100M1002-PCI] ...1 First step guide ...1 CD-ROM \*1 [API-PAC(W32) cTEST] ...1 Synchronization control cable (10cm) ...1

The CD-ROM contains the driver software and User's Guide

#### How to connect the connectors

#### **Connector shape**

To connect an external device to this product, plug the cable from the device into the interface connector (CH0, CH1, CLK, TRG) shown below. This product has the following interface connectors: the (CH0, CH1 connector) for analog inputs, (CLK connector) for reference clock and (TRG connector) for external trigger I/O.

\* Please refer to page 3 for more information on the supported cable.

\* Please refer to page 3 for more information on the supported cable.

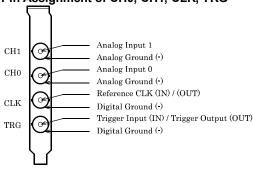

#### Connector Pin Assignment Pin Assignment of CH0, CH1, CLK, TRG

| Analog Input 0 - 1      | Analog input signals. The numbers correspond to channel numbers.                                                                                                                                                                                 |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Analog Ground           | Analog ground common to analog input signals.                                                                                                                                                                                                    |  |  |  |

| Trigger Input<br>(IN)   | External trigger input signal used for sampling start condition<br>and sampling clock etc.<br>Combined use of the external trigger output and the connector.<br>Can be only used as either external trigger input or external<br>trigger output. |  |  |  |

| Trigger Output<br>(OUT) | Outputs internal sampling clock and waveform judgment result<br>as status signal.<br>Combined use of the external trigger input and the connector.<br>Can be only used as either external trigger input or external<br>trigger output.           |  |  |  |

| Reference CLK           | Reference clock I/O signal Can be only used as either input or output.                                                                                                                                                                           |  |  |  |

| Digital Ground          | Digital ground common to digital I/O signals.                                                                                                                                                                                                    |  |  |  |

#### **⚠** CAUTION

Please do not connect the analog ground and the digital ground. The measurement result of the analog signal may be influenced.

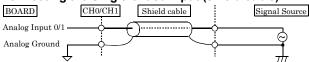

#### **Connecting the Analog Input Signal**

#### Connection Example of Single-ended Input

The following figure shows an example of shield cable connection. Connect BNC connector of CH0/CH1 for each anlog input channel respectively, the wick line to the signal line and the shield braid to the ground.

#### Connecting the Single-ended Input (shield cable)

#### ⚠ CAUTION

Do not touch the external connector (BNC connector) when the power is on. Otherwise this may malfunction, cause a failure due to static electricity.

When high frequency more than 1/2 of the sampling frequency is included in the signal source, alias occurs, and the signal might not be acquired normally.

If this product and the signal source receive noise or the distance between this product and the signal source is too long, data may not be input properly.

The analog signal to be input should not exceed the maximum input voltage (based on this product analog ground). If it exceeds the maximum voltage, this product may be damaged.

Input data remains indeterminate when no input pin is connected. The analog input pin for the channel not connected to the signal source must be connected to the analog ground. Please do not connect terminal resistances such as  $50\Omega$  and  $75\Omega$  instead of short circuit.

When input impedance is  $50\Omega$ , the output current (output voltage/50) from the signal source grows. Please confirm the current value of the connected signal source first.

When the ground is set to input coupling type, please

disconnect signal source from BNC connector first. If you do not so, signal source may fail.

The settings of range setting etc. are unsettled when the PC is started.

Please adjust the input impedance to  $50\Omega$  when the signal reflection etc. are anxious.

However, the effect cannot be achieved except for cases such as setting the output impedance of the signal source to  $50\Omega$ , and setting the characteristic impedance of the used connector/cable etc. to  $50\Omega$ .

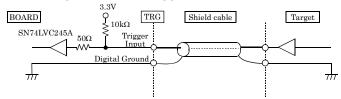

### Connecting the External Trigger I/O Signal

This section shows an example of how to connect external trigger I/O signals (post trigger input signals and sampling clock input signal) using BNC cable.

User can use an optional BNC cable (BNC-Bxxx) to connect your external devices to BNC connector of TRG.

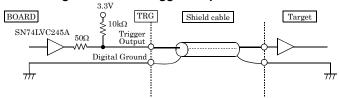

External trigger I/O signal is the positive logical I/O.

These external trigger I/O signals are 3.3VLVTTL level not only for the input but also for the output.

The external trigger I/O signal also can be used as BNC connector of TRG.

Therefore, it can be only used as either the input or the output. Switching I/O can be done by the software.

#### **Connecting the External Trigger Input**

#### **Connecting the External Trigger Output**

### ⚠ CAUTION

Do not connect any output signal to the analog or digital ground. Do not interconnect outputs. Doing either can cause a malfunction.

The signal input of 5VTTL/5VCOMOS is possible.

The input is the default at startup.

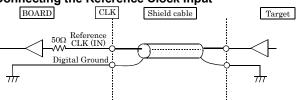

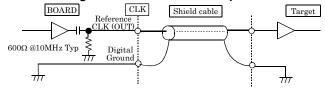

#### Connecting the Reference Clock I/O Signal

This section shows an example of how to connect reference clock I/O signals using BNC cable.

User can use an optional BNC cable (BNC-Bxxx) to connect your external devices to CLK. External trigger I/O signal is the positive logical I/O. All the I/O signals are 3.3VLVTTL level.

In addition, the reference clock I/O signal also can be used as BNC connector of CLK. Therefore, it can be only used as either the input or the output.

Switching I/O can be done by the software.

#### **Connecting the Reference Clock Input**

#### **Connecting the Reference Clock Output**

#### ⚠ CAUTION

Do not connect any output signal to the analog or digital ground. Do not interconnect outputs. Doing either can cause a malfunction.

The input is the default at startup.

The reference clock is a period signal that becomes the standard of the sampling period.

It is possible to expand the number of channels by the synchronization between external instrument or another board with the same type by the reference clock, and measure the mixed signal by the synchronization between other measurement instrument.

Moveover, it is also used in the case of performing sampling at a more accurate period supplied by frequency standards etc.

#### **Connecting the Reference Clock**

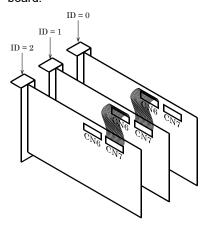

### **Synchronization Control Connectors**

#### **SC Connectors**

Controlling simultaneous operations between boards or controlling in sync with events is in part dependent on software performance. In order to enhance the reliability of the entire system and to solve these problems, the board is equipped with SC (Synchronization Control) connectors (CN6, CN7).

Connecting the SC connectors allows boards of the same or different models to operate in sync with one another.

From the boards connected with the SC cable, select one master board and use others as slaves. On the master board, set the signal to be supplied to the slave boards with the software. On the slave boards, the signal from the master board can be set to either the pacer clock operation start or stop factor.

All board operations can also be stopped with a stop request from the master in case of an error, for example, or when requested from a slave board. A maximum of 16 boards can be connected including the master.

For more information on the setup procedure, see the driver software online help.

# Example 1: When sampling clock start and stop requirements are set the same for multiple boards

In order to synchronize master sampling clock start and stop with slave boards you can build a synchronous system which does not depend on software processing capabilities.

If the board model is the same, data remains synchronized among boards even when channels are expanded. When board models are different, data still remains compatible since sampling clock start and stop are dependent on the master.

- (1) Connect the SC cable.

- (2) Designate master/slave with the software.

- (3) Assign to the connectors the sampling clock start and stop signals to be output from the master.

- (4) Set up slave boards so they can utilize all signals.

- (5) Start in order of slave to master boards.

### ⚠ CAUTION

When sampling clock signals are assigned to the synchronization control connector, the maximum clock frequency is restricted to 5MHz.

When signals are assigned to the synchronization control connector, a delay of approximately 100nsec occurs at the slave board.

## Example 2: When controlling slave operations with master's internal events

By outputting an internal event (interrupt) occurring on the master board, the slaves can start operating in sync with that signal.

- (1) Connect the SC cable.

- (2) Designate master/slave with the software.

- (3) Assign to the connector the event signal to be output from the master.

- (4) Set signals from the master to the start requirements on the slave boards.

- (5) Start in order of slave to master boards.

#### Connecting the SC Connectors (CN6, CN7)

This product is equipped with sync signal control connectors (CN3, CN4) for connecting a sync signal cable. When the cable is connected, multiple boards can operate in sync with one another.

#### **Connection Procedure**

Connect the sync signal cable when two or more boards need to operate in sync with one another. Connect CN6 with a smaller ID number to CN7 with a greater ID number with the cable. You should only use the cable that came with the board.